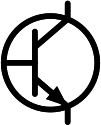

BJTs: DC Analysis#

How do we use the nonlinear VI characteristic to perform circuit analysis?

We can use nodal analysis as we did with the diode but how do we solve the system?

MATLAB or something similar

Load Lines

Some linear assumptions

Let’s work on the linear assumption method first. We assume that the BJT is in the active region. In this region we can use as many of these three assumptions as necessary:

\(V_{BE}=0.7V\)

\(I_C=ßI_B\)

\(I_E=I_C+I_B\)

These assumptions can be made in another form: a D.C. equivalent circuit

Let’s practice this on a simple circuit

Example

Assume the BJT is operating in the active region. Find the Q-point and check the active assumption.

Solution

%% Find node voltages

clear all

close all

clc

format short eng

format compact

Rb=86e3;

Rc=150;

B=200;

syms Va Vb Vc Ib

e(1)=Va==5;

e(2)=Vb==0.7;

e(3)=((Va-Vb)/Rb)-Ib==0;

e(4)=((Va-Vc)/Rc)-B*Ib==0;

sol=solve(e,Va,Vb,Vc,Ib);

Va=eval(sol.Va)

Vb=eval(sol.Vb)

Vc=eval(sol.Vc)

Ib=eval(sol.Ib)

%% check active assumption - Junctions

Vbe=Vb-0

Vbc=Vb-Vc

%% check active assumption - collector/emitter

Vce=Vc-0

Analysis with Load Lines#

Use figures from above

Region |

BE Junction |

BC Junction |

|---|---|---|

Cut-off |

Reverse |

Reverse |

Active |

Forward |

Reverse |

Saturation |

Forward |

Forward |

Checking Assumption in Saturation#

How can we change a value in the circuit to cause it to operate in the saturation region?

Lower \(R_B\)

Raise \(R_C\)

The analysis remains largely the same. Only the values change.

%% Find node voltages

clear all

close all

clc

format short eng

format compact

Rb=1e3;

Rc=150;

B=200;

syms Va Vb Vc Ib

e(1)=Va==5;

e(2)=Vb==0.7;

e(3)=((Va-Vb)/Rb)-Ib==0;

e(4)=((Va-Vc)/Rc)-B*Ib==0;

sol=solve(e,Va,Vb,Vc,Ib);

Va=eval(sol.Va)

Vb=eval(sol.Vb)

Vc=eval(sol.Vc)

Ib=eval(sol.Ib)

%% check active assumption - Junctions

Vbe=Vb-0

Vbc=Vb-Vc

%% check active assumption - collector/emitter

Vce=Vc-0

%% Find node voltages

clear all

close all

clc

format short eng

format compact

Rb=86e3;

Rc=1e3;

B=200;

syms Va Vb Vc Ib

e(1)=Va==5;

e(2)=Vb==0.7;

e(3)=((Va-Vb)/Rb)-Ib==0;

e(4)=((Va-Vc)/Rc)-B*Ib==0;

sol=solve(e,Va,Vb,Vc,Ib);

Va=eval(sol.Va)

Vb=eval(sol.Vb)

Vc=eval(sol.Vc)

Ib=eval(sol.Ib)

%% check active assumption - Junctions

Vbe=Vb-0

Vbc=Vb-Vc

%% check active assumption - collector/emitter

Vce=Vc-0

Checking Assumption in Cut-off#

How can we change a value in the circuit to cause it to operate in the cut-off region?

Raise \(R_B\)

Lower \(R_C\)

The analysis remains largely the same. Only the values change.

%% Find node voltages

clear all

close all

clc

format short eng

format compact

Rb=100e6;

Rc=150;

B=200;

syms Va Vb Vc Ib

e(1)=Va==5;

e(2)=Vb==0.7;

e(3)=((Va-Vb)/Rb)-Ib==0;

e(4)=((Va-Vc)/Rc)-B*Ib==0;

sol=solve(e,Va,Vb,Vc,Ib);

Va=eval(sol.Va)

Vb=eval(sol.Vb)

Vc=eval(sol.Vc)

Ib=eval(sol.Ib)

%% check active assumption - Junctions

Vbe=Vb-0

Vbc=Vb-Vc

%% check active assumption - collector/emitter

Vce=Vc-0

%% Find node voltages

clear all

close all

clc

format short eng

format compact

Rb=86e3;

Rc=5;

B=200;

syms Va Vb Vc Ib

e(1)=Va==5;

e(2)=Vb==0.7;

e(3)=((Va-Vb)/Rb)-Ib==0;

e(4)=((Va-Vc)/Rc)-B*Ib==0;

sol=solve(e,Va,Vb,Vc,Ib);

Va=eval(sol.Va)

Vb=eval(sol.Vb)

Vc=eval(sol.Vc)

Ib=eval(sol.Ib)

%% check active assumption - Junctions

Vbe=Vb-0

Vbc=Vb-Vc

%% check active assumption - collector/emitter

Vce=Vc-0

The problems above are designed to improve your understanding of the regions of operation but the analysis is simple and repetitive. Let’s practice analyzing other circuits.

Examples#

%% Find node voltages

clear all

close all

clc

format short eng

format compact

R1=20e3;

R2=80e3;

Rc=2e3;

Re=1e3;

B=200;

syms Va Vb Vc Ve Ib

e(1)=Va==15;

e(2)=Vb-Ve==0.7;

e(3)=((Va-Vb)/R1)-Ib-((Vb)/R2)==0;

e(4)=Ib-((Ve)/Re)+B*Ib==0;

e(5)=((Va-Vc)/Rc)-B*Ib==0;

sol=solve(e,Va,Vb,Vc,Ve,Ib);

Va=eval(sol.Va)

Vb=eval(sol.Vb)

Vc=eval(sol.Vc)

Ve=eval(sol.Ve)

Ib=eval(sol.Ib)

%% check active assumption - Junctions

Vbe=Vb-Ve

Vbc=Vb-Vc

%% check active assumption - collector/emitter

Vce=Vc-Ve

%% Find node voltages

clear all

close all

clc

format short eng

format compact

R1=100e3;

R2=100e3;

Rc=1e3;

Re=5e3;

B=200;

syms Va Vb Vc Ve Ib

e(1)=Va==15;

e(2)=Vb-Ve==0.7;

e(3)=((Va-Vb)/R1)-Ib-((Vb)/R2)==0;

e(4)=Ib-((Ve)/Re)+B*Ib==0;

e(5)=((Va-Vc)/Rc)-B*Ib==0;

sol=solve(e,Va,Vb,Vc,Ve,Ib);

Va=eval(sol.Va)

Vb=eval(sol.Vb)

Vc=eval(sol.Vc)

Ve=eval(sol.Ve)

Ib=eval(sol.Ib)

%% check active assumption - Junctions

Vbe=Vb-Ve

Vbc=Vb-Vc

%% check active assumption - collector/emitter

Vce=Vc-Ve

%% Find node voltages

clear all

close all

clc

format short eng

format compact

Rf=250e3;

Rc=4.7e3;

Re=1.2e3;

B=90;

syms Va Vb Vc Ve Ib

e(1)=Va==10;

e(2)=Vb-Ve==0.7;

e(3)=((Vc-Vb)/Rf)-Ib==0;

e(4)=Ib-((Ve)/Re)+B*Ib==0;

e(5)=((Va-Vc)/Rc)-B*Ib-((Vc-Vb)/Rf)==0;

sol=solve(e,Va,Vb,Vc,Ve,Ib);

Va=eval(sol.Va)

Vb=eval(sol.Vb)

Vc=eval(sol.Vc)

Ve=eval(sol.Ve)

Ib=eval(sol.Ib)

%% check active assumption - Junctions

Vbe=Vb-Ve

Vbc=Vb-Vc

%% check active assumption - collector/emitter

Vce=Vc-Ve

A PNP Example#

%% Find node voltages

clear all

close all

clc

format short eng

format compact

Rb=580e3;

Rc=5e3;

B=100;

syms Va Vb Vc Ve Ib

e(1)=Va==1.5;

e(2)=Ve-Vb==0.6;

e(3)=Ve==5;

e(4)=((Va-Vb)/Rb)+Ib==0

e(5)=-((Vc)/Rc)+B*Ib==0

sol=solve(e,Va,Vb,Vc,Ve,Ib);

Va=eval(sol.Va)

Vb=eval(sol.Vb)

Vc=eval(sol.Vc)

Ve=eval(sol.Ve)

Ib=eval(sol.Ib)

%% check active assumption - Junctions

Veb=Ve-Vb

Vcb=Vc-Vb

%% check active assumption - collector/emitter

Vec=Ve-Vc